## DJK3C: DIGITAL ELECTRONICS

## Unit I

## Number System:

Decimal – binary – octal – hexadecimal number system – conversion from one system to another – binary arithmetic – 1's complement – 2's complement – BCD, excess 3, gray, alpha numeric codes.

## Unit II

## **Boolean algebra:**

Boolean operation – rules and laws of Boolean algebra – De Morgan's theorems – implication of expressions using Boolean algebra – Karnaugh map.

## Unit III

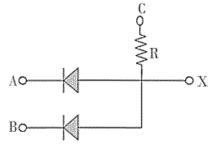

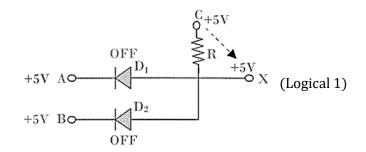

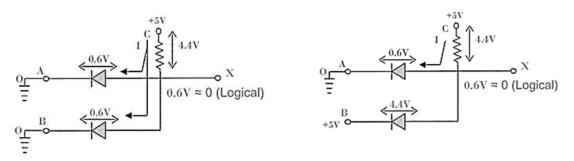

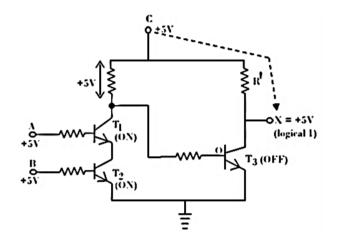

## **Basic Logic gates:**

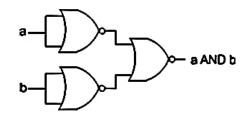

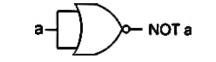

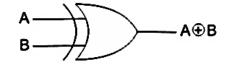

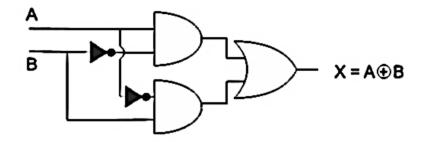

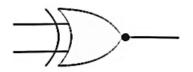

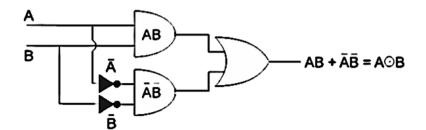

AND, OR, NOT (symbol, truth table, circuit diagram, working) NAND, NOR, EX-OR, EX- NOR (symbol, truth table)

## Unit IV

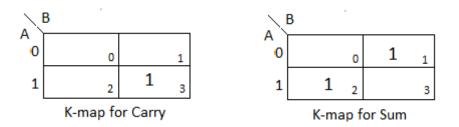

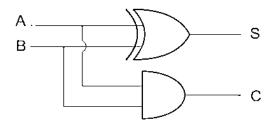

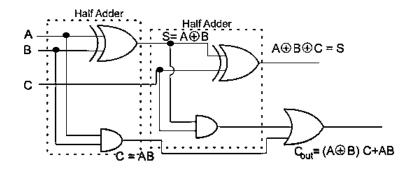

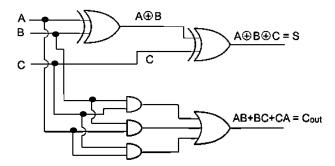

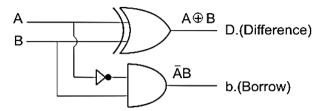

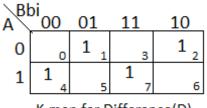

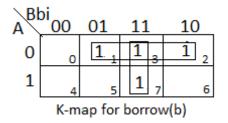

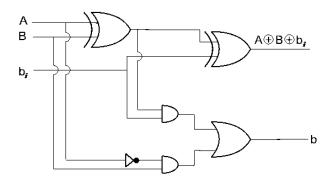

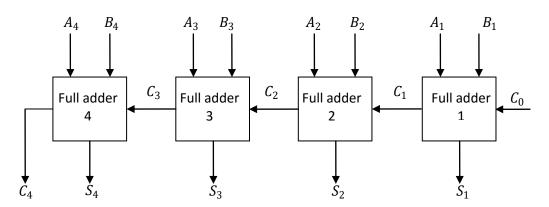

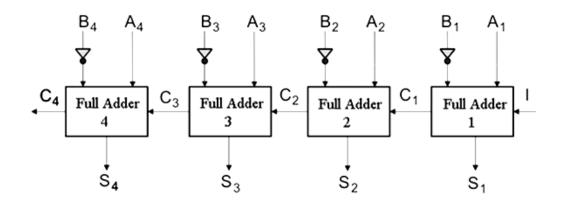

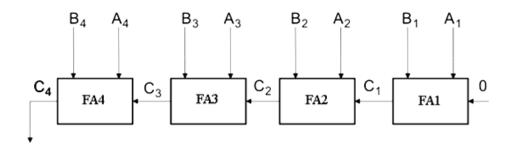

# **Combinational Circuits:**

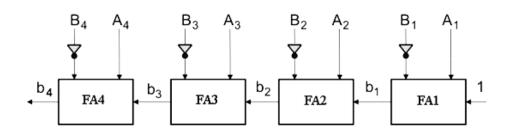

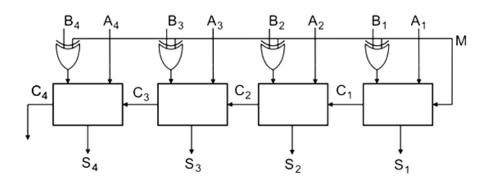

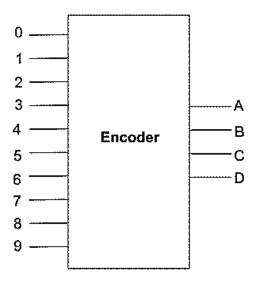

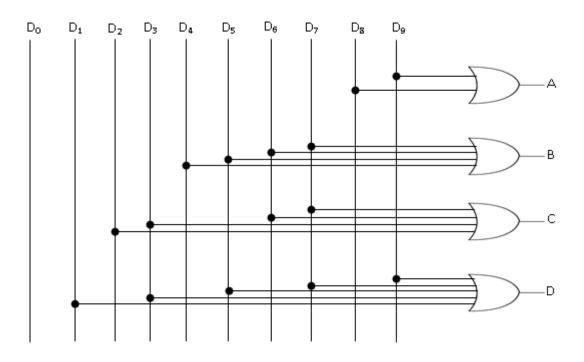

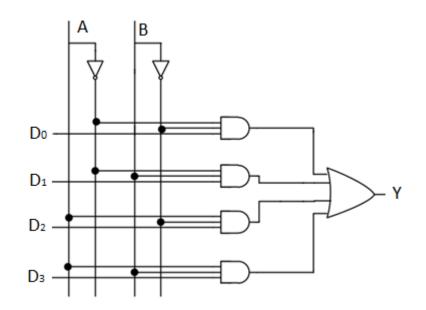

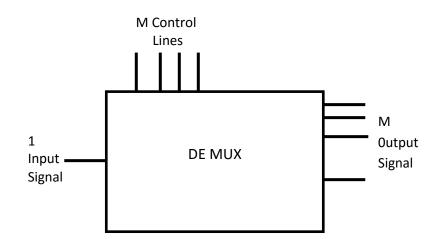

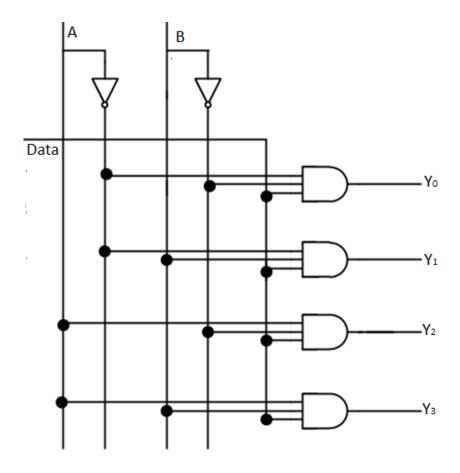

Half adder – full adder – half sub tractor – full sub tractor – binary adder – BCD adder – decoder – encoder – multiplexer – de multiplexer.

## Unit V

## Flip flops:

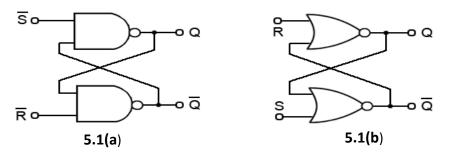

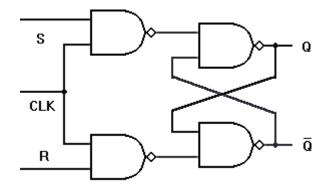

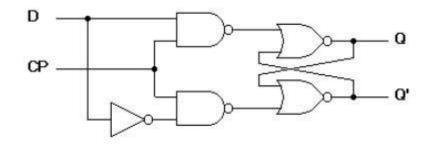

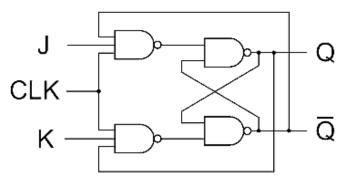

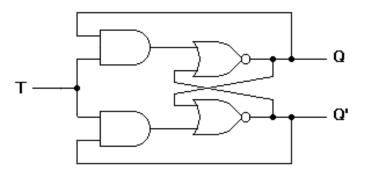

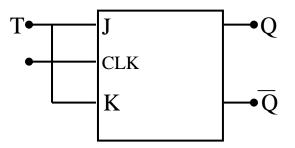

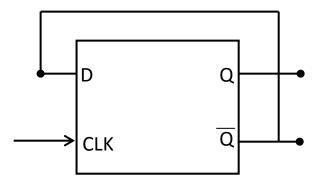

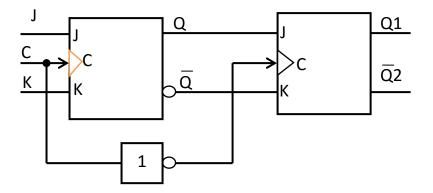

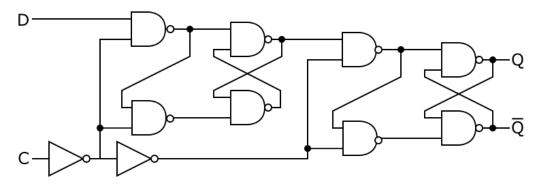

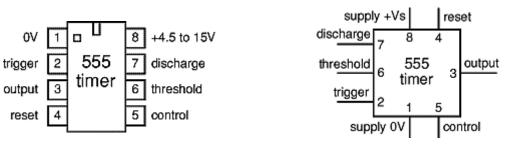

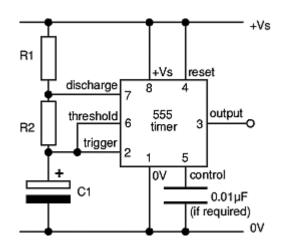

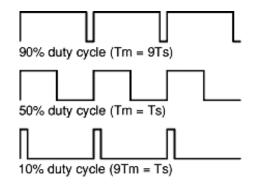

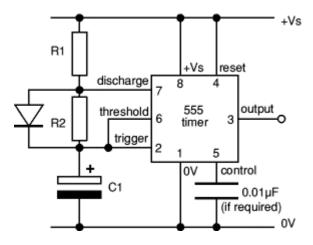

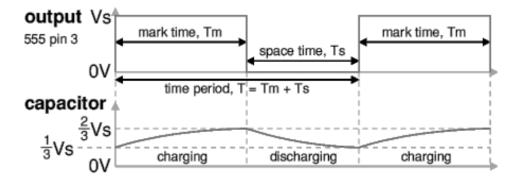

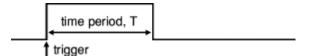

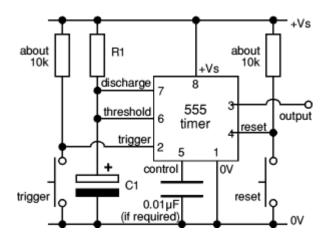

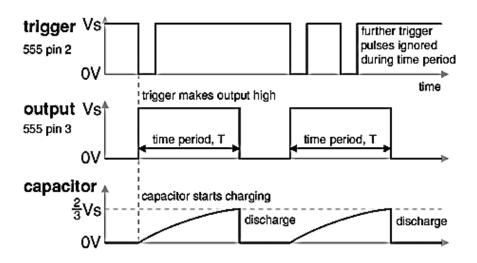

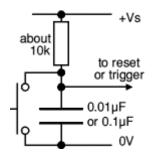

RS, JK, D, T flip flops – master slave flip flop - IC 555 timer – astable multi vibrator - mono stable multi vibrator.

# **Books for study and reference :**

- 1. Digital principles & applications Albert Paul Malvino & Leach

- 2. Digital Logic & Computer Design Morris Mano.

## Unit INumber System

Decimal - Binary- Octal - Hexadecimal number system – conversion from one system to another – Binary arithmetic – 1's complement – 2's complement – BCD, Excess, Gray, Alpha numeric codes

## 1.1 Number System:

A number is a mathematical object used to count, measure, and label. Numbers are represented by a string of digital symbols. A number system of base r is a system that uses distinct symbols for r digits. That is in a positional baser numeral system r basic symbols (or digits) corresponding to the first r natural numbers including zero are used. To generate the rest of the numerals, the position of the symbol in the figure is used. The symbol in the last position has its own value, and as it moves to the left its value is multiplied by r. There are four systems of arithmetic used in digital system. These systems are Decimal, Binary, Hexadecimal and Octal.

| System      | Base | Digits                          |

|-------------|------|---------------------------------|

| Binary      | 2    | 01                              |

| Octal       | 8    | 01234567                        |

| Decimal     | 10   | 0123456789                      |

| Hexadecimal | 16   | 0 1 2 3 4 5 6 7 8 9 A B C D E F |

# 1.2 Decimal Number System:

The Decimal number system has a base ten. This system uses ten distinct digits 0 1 2 3 4 5 6 7 8 9 to form any number. Each digit can be used individually or they can be grouped to form a numeric value.Each of decimal digits, 0 through 9, has a place value or weight depending on its position. The weights are units, tens, hundreds, thousands and so on. The same can be expressed as the powers of its base as  $10^0, 10^1, 10^2, 10^3 \cdots etc$  for the integer partand  $10^{-1}, 10^{-2}, 10^{-3}, 10^{-4} \cdots etc$  for the fractional part.  $10^0, 10^1, 10^2, 10^3 \cdots etc$  represents the units, tens, hundreds, thousands etc. and the quantities  $10^{-1}, 10^{-2}, 10^{-3}, \cdots etc$  represents one tenth, one hundredth, one thousandth etc. The integer part and fractional parts are separated by a decimal point. The position weights in decimal system is given as

|  | 10 <sup>3</sup> | 10 <sup>2</sup> | 10 <sup>1</sup> | 10 <sup>0</sup> |  | $10^{-1}$ | $10^{-2}$ | $10^{-3}$ | $10^{-4}$ | ••• |  |

|--|-----------------|-----------------|-----------------|-----------------|--|-----------|-----------|-----------|-----------|-----|--|

|--|-----------------|-----------------|-----------------|-----------------|--|-----------|-----------|-----------|-----------|-----|--|

Example:

(i)

$$7693 = 7 \times 10^3 + 6 \times 10^2 + 9 \times 10^1 + 3 \times 10^0$$

=  $7 \times 1000 + 6 \times 100 + 9 \times 10 + 3 \times 1$

=  $7000 + 600 + 90 + 3$

(ii)  $1936.46 = 1 \times 10^3 + 9 \times 10^2 + 3 \times 10^1 + 6 \times 10^0 + 4 \times 10^{-1} + 6 \times 10^{-2}$

=  $1000 + 900 + 30 + 6 + 0.4 + 0.06$

#### 1.3 Binary Number System:

The base of the binary number system is two. It uses the digits0 and 1 only. The two digits 0 and 1 are called a bit. The place value of each position can be expressed in terms of powers of 2 like  $2^0$ ,  $2^1$ ,  $2^2$ , *etc* for integer part and  $2^{-1}$ ,  $2^{-2}$ ,  $2^{-3}$ , *etc* for the fractional part. A binary point separates the integer and fractional part. The position weights in the binary is given as

|  | , | 2 <sup>3</sup> | 2 <sup>2</sup> | 2 <sup>1</sup> | 2 <sup>0</sup> |  | $2^{-1}$ | $2^{-2}$ | 2 <sup>-3</sup> | $2^{-4}$ | ••• |

|--|---|----------------|----------------|----------------|----------------|--|----------|----------|-----------------|----------|-----|

|--|---|----------------|----------------|----------------|----------------|--|----------|----------|-----------------|----------|-----|

4 bit binary word ⇒ nibble

8 bit binary word ⇒ byte

16 bit binary word ⇒ word

32 bit binary word ⇒ double word

#### 1.4 Octal Number System:

The base of the octal number system is eight. It uses eight digits 0 1 2 3 4 5 6 and 7 to form a number. The place value of each position can be expressed in terms of powers of 8 like  $8^0, 8^1, 8^2, etc$  for integer part and  $8^{-1}, 8^{-2}, 8^{-3}, etc$  for the fractional part. An octal point separates the integer and fractional part. Sets of 3-bit binary numbers can be represented by octal numbers (000, 001, 010, 011, 100, 101, 110, 111) and this can be conveniently be used for entering data in the computer. The position weights in the octal system is given as

| ••• | 8 <sup>3</sup> | 8 <sup>2</sup> | 8 <sup>1</sup> | 80 |  | 8 <sup>-1</sup> | 8 <sup>-2</sup> | 8-3 | 8 <sup>-4</sup> |  |

|-----|----------------|----------------|----------------|----|--|-----------------|-----------------|-----|-----------------|--|

|-----|----------------|----------------|----------------|----|--|-----------------|-----------------|-----|-----------------|--|

## 1.5 Hexadecimal Number System:

The Hexadecimal number system has a base of 16. It has 16 distinct digit symbols. It uses the digits  $0\ 1\ 2\ 3\ 4\ 5\ 6\ 7\ 8\ 9\,$  plus the letters  $A\ B\ C\ D\ E\ and\ F$ . Any hexadecimal digit can be represented by a group of four bit binary sequence. That is the Hexadecimal numbers are represented by sets of 4-bit binary sequence (0000, 0001,0010, 0011, 0100,0101,0110, 0111,1100,1101,1110,1111). The position weight in the hexadecimal number system is given as

| ••• | 16 <sup>3</sup> | 16 <sup>2</sup> | 16 <sup>1</sup> | 16 <sup>0</sup> |  | 16 <sup>-1</sup> | 16 <sup>-2</sup> | 16 <sup>-3</sup> | $16^{-4}$ | ••• |

|-----|-----------------|-----------------|-----------------|-----------------|--|------------------|------------------|------------------|-----------|-----|

|-----|-----------------|-----------------|-----------------|-----------------|--|------------------|------------------|------------------|-----------|-----|

## Number System

| Decimal   | Binary   | Octal    | Hexadecimal |

|-----------|----------|----------|-------------|

| (Base 10) | (Base 2) | (Base 8) | (Base 16)   |

| 0         | 0000     | 00       | 0           |

| 1         | 0001     | 01       | 1           |

| 2         | 0010     | 02       | 2           |

| 3         | 0011     | 03       | 3           |

| 4         | 0100     | 04       | 4           |

| 5         | 0101     | 05       | 5           |

| 6         | 0110     | 06       | 6           |

| 7         | 0111     | 07       | 7           |

| 8         | 1000     | 10       | 8           |

| 9         | 1001     | 11       | 9           |

| 10        | 1010     | 12       | A           |

| 11        | 1011     | 13       | В           |

| 12        | 1100     | 14       | С           |

| 13        | 1101     | 15       | D           |

| 14        | 1110     | 16       | E           |

| 15        | 1111     | 17       | F           |

## 1.6 Decimal to Binary Conversion:

Decimal number can be converted to binary by repeatedly dividing the number by 2 for integer part and collecting the reminders. The remainders can be written in the reverse order (from bottom to top) to get binary result. For fractional part, it has to be multiplied by 2 successively and collecting the carries, to write from top to bottom. The multiplication is repeated till the fractional part becomes zero or the required number of significant bit is obtained.

1. Convert  $(19)_{10}$  into its Binary equivalent

2 19

2 9 1

2 9 1

2 2 0

1 0

1 0

MSB (Most Significant Bit)

$$10001_{LSB}$$

$10011_{LSB}$

2. Convert $(0.625)_{10}$  into its Binary equivalent

$\begin{array}{c} 0.625 \times 2 = 1.250 \ carry \ is \ 1 \\ 0.250 \times 2 = 0.500 \ carry \ is \ 0 \\ 0.500 \times 2 = 1.000 \ carry \ is \ 1 \\ (LSB) \\ (0.625)_{10} = \ (0.101)_2 \end{array}$

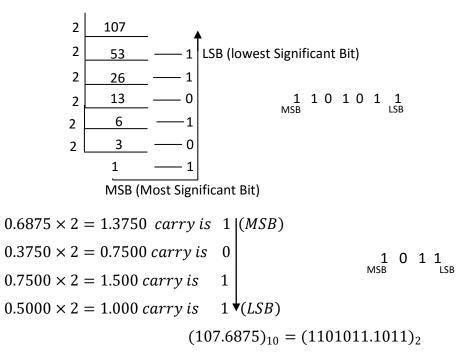

3. Convert  $(107.6875)_{10}$  to its equivalent Binary

#### 1.7 Binary to Decimal Conversion:

A binary number can be converted into decimal number by adding the products of eachbitanditscorresponding weight.

Example:

(i)

$$(101)_2 = 1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0$$

$= 4 + 0 + 1$

$= (5)_{10}$

(ii)  $(10011)_2 = 1 \times 2^4 + 0 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 1 \times 2^0$

$= 16 + 0 + 0 + 2 + 1$

$= (19)_{10}$

(iii)  $(0.101)_2 = 1 \times 2^{-1} + 0 \times 2^{-2} + 1 \times 2^{-3}$

$= 1 \times 0.5 + 0 + 1 \times 0.125$

$= 0.5 + 0 + 0.125$

$= (0.625)_{10}$

(iv)  $(1101011.1011)_2$

(1101011)<sub>2</sub> =  $1 \times 2^6 + 1 \times 2^5 + 0 \times 2^4 + 1 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 1 \times 2^1$

$= 64 + 32 + 0 + 8 + 0 + 2 + 1$

$= (107)_{10}$

(0.1011)  $= 1 \times 2^{-1} + 0 \times 2^{-2} + 1 \times 2^{-3} + 1 \times 2^{-4}$

$= 0.5 + 0 + 0.125 + 0.0625$

$$= 0.5 + 0 + 0.125 + 0.0625$$

$$= (0.6875)_{10}$$

$$\therefore (1101011.1011)_2 = (107.6875)_{10}$$

1.8 Hexadecimal to Decimal:

A hexadecimal number can be converted into decimal number by adding the products of each digit and its corresponding weight. The weights are power of 16. Example:

1. Convert hexadecimal  $(D5)_{16}$  to decimal

$$(D5)_{16} = (13 \times 16^{1} + 5 \times 16^{0}) \implies (D)_{16} = (13)_{10}$$

$$= 13 \times 16 + 5 \times 1$$

$$= 208 + 5$$

$$= (213)_{10}$$

$$ie., (D5)_{16} = (213)_{10}$$

2. Convert hexadecimal  $(3FC.8)_{16}$  to decimal  $(3FC.8)_{16} = (3 \times 16^2 + 15 \times 16^1 + 12 \times 16^0 + 8 \times 16^{-1})$   $\Rightarrow (F)_{16} = (15)_{10} \& (C)_{16} = (12)_{10}$   $= 3 \times 256 + 15 \times 16 + 12 \times 1 + 8 \times \frac{1}{16}$  = 768 + 240 + 12 + 0.5  $= (1020.5)_{10}$  $ie., (3FC.8)_{16} = (1020.5)_{10}$

#### 1.9 Decimal to Hexadecimal:

Decimal number can be converted to hexadecimal by repeatedly dividing the number by 16 for integer part and collecting the reminders. The remainders can be written in the reverse order (from bottom to top) to get hex result. For fractional part, it has to be multiplied by 16 successively and collecting the carries, to write from top to bottom. The multiplication is repeated till the fractional part becomes zero or the required numbers of significant digits are obtained.

Example:

1. Convert  $(1020)_{10}$  to hexadecimal

16 1020

16 63 12

$$\leftarrow$$

C LSB (lowest Significant Bit)

3 15  $\leftarrow$  F MSB (Most Significant Bit)

MSB (Most Significant Bit)

$$(1020)_{10} = (3FC)_{16}$$

2. Convert  $(98.625)_{10}$  to hexadecimal

1.10 HexadecimaltoBinary:

Hexadecimal numbers can be converted into binary numbers by converting each hexadecimal digit to its 4-bit binary equivalent

Α

1. Convert  $(25)_H$  to Binary

$$(25)_H = \left(\underbrace{0010}_2 \underbrace{0101}_5\right)_2$$

2. Convert  $(3A.7)_H$  to Binary

$$(3A)_{H} = \left(\underbrace{0011}_{3}\underbrace{1010}_{A}\right)_{2}$$

$$(.7)_{H} = \left(\underbrace{.0111}_{7}\right)_{2}$$

$$(3A.7)_{H} = \left(\underbrace{0011}_{3}\underbrace{1010}_{A} \cdot \underbrace{0111}_{7}\right)_{2}$$

3. Convert  $(CD. E8)_H$  to Binary

$$(CD)_{H} = \left(\underbrace{1100}_{C} \underbrace{1101}_{D}\right)_{2}$$

(.E8)\_{H} =  $\left(\underbrace{.1110}_{E} \underbrace{1000}_{8}\right)_{2}$

(CD.E8)\_{H} =  $\left(\underbrace{1100}_{C} \underbrace{1101}_{D} \cdot \underbrace{1110}_{E} \underbrace{1000}_{8}\right)_{2}$

## 1.11 Binary to Hexadecimal:

Conversion from binary to hexadecimal is easily accomplished by partitioning the binary number into groups of four binary digits, starting from the binary point to the left and to the right. It may be necessary to add zeros to the last group, if it does not end in exactly four bits. Each group of 4-bits binary must be represented by its hexadecimal equivalent.

1.

$$(1010 \cdot 1101)_2 = (A \cdot D)_H$$

- 2.  $(110 \cdot 101)_2 = (0110 \cdot 1010)_2 = (6 \cdot A)_H$

- 3.  $(1110 \cdot 11)_2 = (1110 \cdot 1100)_2 = (E \cdot C)_H$

## 1.12 Octal to Decimal:

Anoctal number can be converted into decimal number by adding the products of each digit and its corresponding weight. The weights are power of 8.

1.

$$(75)_8 = 7 \times 8^1 + 5 \times 8^0$$

$$= 56 + 5$$

= (61)<sub>10</sub>

2. (45 \cdot 6)<sub>8</sub> = 4 \times 8<sup>1</sup> + 5 \times 8<sup>0</sup> + 6 \times 8<sup>-1</sup>

= 32 + 5 + 0.75

= (37.75)<sub>10</sub>

## 1.13 Decimal to octal:

Decimal number can be converted to octal by repeatedly dividing the number by 8 for integer part and collecting the reminders. The remainders can be written in the reverse order (from bottom to top) to get octal result. For fractional part, it has to be multiplied by 8 successively and collecting the carries, to write from top to bottom. The multiplication is repeated till the fractional part becomes zero or the required numbers of significant digits are obtained.

1. Convert  $(68)_{10}$  to octal

2. Convert (98.625)<sub>10</sub>to Octal

$0.625 \times 8 = 5.0000$  carry is 5

$$(98.625)_{10} = (142.5)_8$$

#### 1.14 Octal to Binary:

Octal numbers can be converted into binary numbers by converting each octal digit to its 3bit binary equivalent

1.

$$(27)_8 = \left(\underbrace{010}_2 \underbrace{111}_7\right)_2$$

2.  $(135)_8 = \left(\underbrace{001}_1 \underbrace{011}_3 \underbrace{101}_5\right)_2$

5.  $(155)_8 = \left(\underbrace{100}_1 \underbrace{011}_3 \underbrace{101}_5\right)_2$

3.

$$(45.5)_8 = \left(\underbrace{100}_4 \underbrace{101}_5 \cdot \underbrace{101}_5\right)_2$$

# 1.15 Binary to Octal:

Conversion from binary to octal is the simplest procedure by grouping the binary number into groups of three binary digits, starting from the binary point to the left and to the right. It may be necessary to add zeros to the last group, if it does not end in exactly three bits. Each group of 3-bits binary must be represented by its octal equivalent.

1.

$$(10\ 101)_2 = (010\ 101)_2 = (25)_8$$

2.

$$(101011)_2 = (101 \ 011)_2 = (53)_8$$

3.

$$(11110.11)_2 = (011 \ 110 \ . \ 110)_2 = (36.6)_8$$

4.

$$(11011011.1111)_2 = (011\ 011\ 011.\ 111\ 100)_2 = (333.74)_8$$

# 1.16 Hexadecimal to Octal:

This can be achieved by first writing down the four bit binary equivalent of hexadecimal digit and then partitioning it into group of 3 bits each. Finally, the three bit octal equivalent is written down.

Example:

1. Convert  $(2AB.9)_H$  to octal Hexa decimal Number  $\rightarrow$ 2 В 9 Α ↓ ↓ ſ ↓ 4 bit Binary Number 0010 1010 1011 1001  $\rightarrow$ 3 bit Partition 001 010 101 011 100 100  $\rightarrow$ Ť ↓ ↓ Ť ſ T Octal Number 1 2 5 3  $\rightarrow$ 4 4  $\therefore$  (2*AB*.9)<sub>16</sub> = (1253.44)<sub>8</sub> 2. Convert  $(3FC.82)_H$  to octal F Hexa decimal Number  $\rightarrow$ С 2 3 8 . Ť ↓ Ť ↓ ſ 4 bit Binary Number  $\rightarrow$ 0011 1111 1100 1000 0010 . 3 bit Partition 100 000 100 001 111 111 100 ↓ ſ ſ ſ Ť ſ ↓ Octal Number 1 7 7 4 4 0 4  $\rightarrow$  $\therefore$  (3FC.82)<sub>16</sub> = (1253.44)<sub>8</sub>

## 1.17 Octal to Hexadecimal:

This can be achieved by first writing down the three bit binary equivalent of octal digit and then partitioning it into group of 4 bits each. Finally, the four bit hexadecimal equivalent is written down.

1. Convert  $(16.2)_8$  to Hexadecimal

octal Number  $\rightarrow$  1 6. 2 ſ ↓. ſ 110 . 010 3 bit Binary  $\rightarrow$ 001 ↓ ↓. Ţ 4 bit Partition  $\rightarrow$ 0000 1110 0100 . Ť Ť ↓ *Hex Number* 0 Ε 4  $\rightarrow$

$\therefore$  (16.2)<sub>8</sub> = (0*E*.4)<sub>16</sub> = (*E*.4)<sub>*H*</sub>

A zero is added to the right most group to make it a group of 4 bits and left most zeros are dropped

2. Convert  $(764.352)_8$  to Hexadecimal

$\therefore (764.352)_8 = (1F4.750)_{16} = (1F4.75)_H$

## 1.18 Binary Arithmetic:

Arithmetic operations such as addition, subtraction, multiplication and division can be performed on binary numbers.

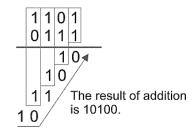

## 1.18.1 Binary addition:

The addition of two Binary numbers is very similar to addition of two decimal numbers. It is key to binary subtraction, multiplication and division. The following rules are followed while adding two binary numbers.

| Augen<br>(A) (B |     | Addend | Carry<br>(A) (B) | Sum | Result                        |

|-----------------|-----|--------|------------------|-----|-------------------------------|

| 0               | +   | 0      | 0                | 0   | 0                             |

| 0               | +   | 1      | 0                | 1   | 1                             |

| 1               | +   | 0      | 01               |     | 1                             |

| 1               | +   | 1      | 1                | 0   | 10 ; read as 0 with a carry 1 |

| 1               | + 1 | . +1   | 1                | 1   | 11 ; read as 1 with a carry 1 |

Example:

1. Add the binary numbers (i) 1011 and 1110  $\,$  (ii) 10.001 and 11.110  $\,$

| (i) | Binary Number          | Equivalent Decimal |

|-----|------------------------|--------------------|

|     | 111 C <del>arr</del> y |                    |

|     | 1011                   | 11                 |

|     | + 1110                 | 14                 |

|     | Sum= 11001             | 25                 |

| (::) | Binary Number | Equivalent Decimal |

|------|---------------|--------------------|

| (ii) | 1 🔶 Carry     |                    |

|      | 10.001        | 2.125              |

|      | + 11.110      | + 3.750            |

|      | Sum= 101.111  | 5.875              |

# 1.18.2 Binary subtraction:

The subtraction of two Binary numbers is very similar to subtraction of two decimal numbers. Subtraction is the inverse operation of addition. The following rules are used in subtracting two binary numbers.

| Min | uend | - 9 | Subtrahend | Differe | ence l | Borrow                             |

|-----|------|-----|------------|---------|--------|------------------------------------|

| 0   |      | -   | 0          | 0       |        | 0                                  |

| 1   |      | -   | 0          | 1       |        | 0                                  |

| 1   | -    |     | 1          | 0       | 0      |                                    |

| 0   | -    |     | 1          | 1       | 1      | read as difference 1 with borrow 1 |

Example:

1. Subtract the binary numbers (i) 101 from 1001 (ii) 11and 10000

| (ii) | Binary Number | r     | Equivalent Decimal |

|------|---------------|-------|--------------------|

| (11) |               | 10000 | 16                 |

|      | -             | 11    | - 3                |

|      | Difference =  | 1101  | 13                 |

# 1.18.3 Binary Multiplication:

Themultiplication of two Binary numbers is very similar to multiplication of two decimal numbers. The following rules are used to multiply two binary numbers.

(i)  $0 \times 0 = 0$ (ii)  $0 \times 1 = 0$ (iii)  $1 \times 0 = 0$ (iv)  $1 \times 1 = 1$

# Example:

Multiply the following binary numbers (i) 1011 and 1101 and (ii) 1.01 and 10.1

| (i) | Binary Multiplication | Equivalent decimal |

|-----|-----------------------|--------------------|

|     | Multiplicand 1011     | 11                 |

|     | Multiplier × 1101     | × 13               |

|     | 1011                  | 33                 |

|     | 0000                  | 11                 |

|     | 1011                  | 143                |

|     | 1011                  |                    |

|     | 10001111              |                    |

| (ii) | Binary Multiplication<br>Multiplicand 1.01 | Equivalent decimal<br>1.25 |

|------|--------------------------------------------|----------------------------|

|      | Multiplier $\times$ 10.1                   | ×2.5                       |

|      | 101                                        | 625                        |

|      | 000                                        | 240                        |

|      | 101                                        | 3025                       |

|      | 11001                                      |                            |

|      | 11.001                                     | 3.025                      |

# 1.18.4 Binary Division:

The division in Binary is exactly same as in decimal. The division by 0 is not allowed. The binary division has only two rules.

(i)  $0 \div 1 = 0$  and (ii)  $1 \div 1 = 1$

Example:

(ii)

Divide the binary numbers (i) 11001 by 101 (ii) 1010 by 100

| Binary Division         | Equivalent decimal                                     |

|-------------------------|--------------------------------------------------------|

| 10.1<br>100 1010<br>100 | $4 \boxed{\begin{matrix} 2.5 \\ 10 \\ 8 \end{matrix}}$ |

| 00100                   | 20                                                     |

| 100                     | 20                                                     |

| 00000                   | 0                                                      |

# 1.19 Complements:

Complements are used in digital computers for simplifying the subtraction operation and for logical manipulation. There are two types of complements, one isr's complement and another is (r - 1)'s complement, where r is base of the system. For binary system the base r is 2, therefore 2's complement and 1's complement is possible.

# 1.19.1 1's complement:

1's complement of a binary number is formed by simply changing each 1in the number to 0 and each 0 in the number to 1.

# Example:

| Binary Number          | Equivalent 1's complement |  |  |  |

|------------------------|---------------------------|--|--|--|

| 1011 $\Rightarrow$     | 0100                      |  |  |  |

| 110001 $\Rightarrow$   | 001110                    |  |  |  |

| 100100 $\Rightarrow$   | 011011                    |  |  |  |

| $11001110 \Rightarrow$ | 00110001                  |  |  |  |

| 1010110 $\Rightarrow$  | 01010010                  |  |  |  |

# 1.19.2 1's complement Subtraction:

(i) To subtract a smaller number from a larger number, the procedure is as follows:

- 1. Determine the 1's complement of the smaller number.

- 2. Add the 1's complement to the larger number

- 3. Remove the carry and add to the sum. The carry is called end-around carry.

The number of bits in the minuend and subtrahend must be equal.

Example:

1. Subtract  $(01110)_2$  from  $(10001)_2$  using 1's complement

| Direct Method of   | 1's complement method of            | Equivalent Decimal |  |  |

|--------------------|-------------------------------------|--------------------|--|--|

| binary subtraction | subtraction                         | subtraction        |  |  |

| 10001              | 10001                               | 17                 |  |  |

| - 01110            | + 10000 (1's complement of 10001)   | - <u>14</u>        |  |  |

| 00011              | (200010(end-around carry1)          | 3                  |  |  |

|                    | $\rightarrow +1$ (add carry to sum) |                    |  |  |

|                    | 00011                               |                    |  |  |

2. Subtract  $(101101)_2$  from  $(110011)_2$  using 1's complement

| Direct Method of   | 1's complement method of           | Equivalent Decimal |  |

|--------------------|------------------------------------|--------------------|--|

| binary subtraction | subtraction                        | subtraction        |  |

| 110011             | 110011                             | 51                 |  |

| - 101101           | + 010010(1's complement of 101101) | - 45               |  |

| 000110             | 4000101 (end-around carry1)        | <u>6</u>           |  |

|                    | +1 (add carry to sum)              |                    |  |

|                    | 000110                             |                    |  |

(ii) To subtract a larger number from a smaller binary number , the procedure is as follows

- 1. Determine the 1's complement of the larger number.

- 2. Add the 1's complement to the smaller number

- 3. The answer has an opposite sign and is the result. There is no carry

Example:

$1.Subtract(10010)_2$  from  $(1100)_2$  using 1's complement

| Direct Method of   | 1's complement method of                 | Equivalent Decimal |  |

|--------------------|------------------------------------------|--------------------|--|

| binary subtraction | subtraction                              | subtraction        |  |

| 01100              | 01100                                    | 51                 |  |

| - 10010            | - 10010 + 01101(1's complement of 10010) |                    |  |

| - 00110            | - 00110 11001                            |                    |  |

|                    | put – sign and take 1's complement for   |                    |  |

|                    | the sum we get , -00110                  |                    |  |

2. Subtract  $(1101)_2$  from  $(1010)_2$  using 1's complement

| Direct Method of   | 1's complement method of               | Equivalent Decimal |  |

|--------------------|----------------------------------------|--------------------|--|

| binary subtraction | subtraction                            | subtraction        |  |

| 1010               | 1010                                   | 10                 |  |

| - 1101             | + 0010(1's complement of 1101)         | - 13               |  |

| - 0011             | 1100                                   | - 3                |  |

|                    | put – sign and take 1's complement for |                    |  |

|                    | the sum we get , -0011                 |                    |  |

# 1.19.2 2's Complement:

The 2's complement of a binary number is formed by taking 1's complement of the number and adding 1 to the least significant bit (LSB) position

2's complement = 1's complement + 1

Example:

Write 2's complement of a binary number  $(1010)_2$

1's complement of 1010 = 0101 Add 1 = +12's complement of 1010 = 0110

Some more Example:

| Binary Number |               | 1's complement | 2's complement |

|---------------|---------------|----------------|----------------|

| 1011          | $\Rightarrow$ | 0100⇒          | 0101           |

| 110001        | $\Rightarrow$ | 001110⇒        | 001111         |

| 100100        | $\Rightarrow$ | 011011⇒        | 011100         |

| 11001110      | $\Rightarrow$ | 00110001⇒      | 00110010       |

| 1010110       | $\Rightarrow$ | 01010010⇒      | 01010011       |

## 1.20 Binary coded System:

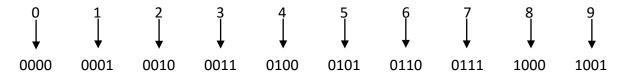

In general, coding is the process of assigning a group of binary digits to represent multivalued items of information. Binary coded decimal (BCD) is a system of writing numerals that assigns a four-digit binary code to each digit 0 through 9 in a decimal (base-10) numeral. The four-bit BCD code for any particular single base-10 digit is its representation in binary notation, as follows:

Numbers larger than 9, having two or more digits in the decimal system, are expressed digit by digit, For example, the BCD interpretation of the base-10 number 1895 is

1 8 9 5 ie., 1895 = 0001 1000 1001 0101

0001 1000 1001 0101

The binary equivalents of 1, 8, 9, and 5, always in a four-digit format, go from left to right.

Binary codes are broadly classified into Numeric codes, Alphanumeric codes and Error detecting codes. Numeric codes are further classified into weighted codes and non-weighted codes. The most obvious way of encoding digits is "natural BCD" (NBCD), where each decimal digit is represented by its corresponding four-bit binary value. This is also called "8421" encoding.Standard binary coded decimal code is commonly known as a weighted 8421 BCD code, with 8, 4, 2 and 1 representing the weights of the different bits starting from the most significant bit (MSB) and proceeding towards the least significant bit (LSB). The weights of the individual positions of the bits of a BCD code are:  $2^3 = 8$ ,  $2^2 = 4$ ,  $2^1 = 2$ ,  $2^0 = 1$ .

The main advantage of the Binary Coded Decimal system is that it is a fast and efficient system to convert the decimal numbers into binary numbers as compared to the pure binary system However, the disadvantage is that BCD code is inefficient as the states between 1010(decimal 10), and 1111 (decimal 15) are not used.

In non-weighted code, there is no positional weight i.e. each position within the binary number is not assigned a prefixed value. No specific weights are assigned to bit position in non –weighted code. The non-weighted codes are classified to

a) The Excess-3 codeb) The Gray code

## 1.21Excess-3 code:

Excess-3 code is an important BCD code, is a 4 bit code and used with BCD numbers as weights are not assigned, it is a kind of non- weighted codes. Excess-3 code was used on some older computers, cash registers and hand held portable electronic calculators. The Excess-3 code for a given decimal number is determined by adding '3' to each decimal digit in the given number and then replacing each digit of the newly found decimal number by its four bit binary equivalent. The table gives the Excess-3 code.

| Decimal | 8421 | Excess-3 |

|---------|------|----------|

| 0       | 0000 | 0011     |

| 1       | 0001 | 0100     |

| 2       | 0010 | 0101     |

| 3       | 0011 | 0110     |

| 4       | 0100 | 0111     |

| 5       | 0101 | 1000     |

| 6       | 0110 | 1001     |

| 7       | 0111 | 1010     |

| 8       | 1000 | 1011     |

| 9       | 1001 | 1100     |

1.21.1 Decimal to Excess-3 code:

Excess-3 code of 24 is obtained as

| 2   | 4                  |                                                          |

|-----|--------------------|----------------------------------------------------------|

| +3  | +3                 |                                                          |

| 5   | 7                  |                                                          |

| 010 | 1 012              | 11                                                       |

| Thu | is, Exe            | cess-3 code of 24 is 0101 0111.                          |

| Sim | ilarly             | , Excess-3 code for (597) $_{10}$ and (14.57) $_{10}$ is |

| (59 | 7) <sub>10</sub> = | (100011001010)                                           |

| (14 | .57) <sub>10</sub> | e = (01000111.10001010)                                  |

|     |                    |                                                          |

# 1.21.2 Excess-3 to Decimal:

From given Excess-3 code, the equivalent decimal number can be determined by first splitting the number into four-bit groups, starting from radix point and then subtracting 0011 from each four-bit group. This gives us 8421 BCD equivalent of the given Excess-3 code, which can then be converted into the equivalent decimal number.

Example:

Determine the decimal equivalent for the Excess-3 code 1000110.

# 0100 0110

# Then Subtracting 0011 from each group,

|   | 0100 | 0110 |      |

|---|------|------|------|

| - | 0011 | -    | 0011 |

|   | 0001 |      | 0011 |

The new number as 00010011. Its decimal equivalent is 13.

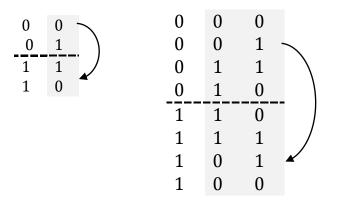

# 1.22 Gray code:

The Gray code was designed by *Frank Gray* at Bell Labs in 1953. It belongs to a class of codes called the minimum change code. The successive coded characters never differ in more than one-bit. The Gray code is a non-weighted code. Because of this, the gray code is not suitable for arithmetic operations but finds applications in input/output devices, some analog-to-digital converters and designation of rows and columns in Karnaugh map etc.

A three-bit gray code can be obtained by merely reflecting the two-bit code about an axis at the end of the code and assigning a third-bit as 0 above the axis and as 1 below the axis. The reflected gray code is nothing but code written in reverse order. By reflecting three-bit code, a four-bit code may be obtained. Process of obtaining 3 bit Gray code by reflecting 2 bit Gray code:

Process of obtaining 4 bit Gray code by reflecting 3 bit Gray code:

| Decimal | Binary | Gray | Code | 2 |   |   |

|---------|--------|------|------|---|---|---|

| 0       | 0000   | 0    | 0    | 0 | 0 |   |

| 1       | 0001   | 0    | 0    | 0 | 1 |   |

| 2       | 0010   | 0    | 0    | 1 | 1 |   |

| 3       | 0011   | 0    | 0    | 1 | 0 |   |

| 4       | 0100   | 0    | 1    | 1 | 0 | ١ |

| 5       | 0101   | 0    | 1    | 1 | 1 |   |

| 6       | 0110   | 0    | 1    | 0 | 1 |   |

| 7       | 0111   | 0    | 1    | 0 | 0 |   |

| 8       | 1000   | 1    | 1    | 0 | 0 |   |

| 9       | 1001   | 1    | 1    | 0 | 1 |   |

| 10      | 1010   | 1    | 1    | 1 | 1 |   |

| 11      | 1011   | 1    | 1    | 1 | 0 |   |

| 12      | 1100   | 1    | 0    | 1 | 0 |   |

| 13      | 1101   | 1    | 0    | 1 | 1 |   |

| 14      | 1110   | 1    | 0    | 0 | 1 |   |

| 15      | 1111   | 1    | 0    | 0 | 0 |   |

## 1.22.1 Decimal to Gray code conversion:

Example

1. Covert  $(39)_{10}$  to gray code

The Gray code equivalent of decimal number 3 and 9 is  $\frac{0010}{3}$   $\frac{1101}{9}$

The four-bit gray code for decimal number  $(39)_{10} \Rightarrow (00101101)_{Gray \ code}$ .

Similarly, gray code for  $(923.1)_{10}$  and (327) is

(923.1)<sub>10</sub> = (1101 0011 0010.0001) Gray code

(327)<sub>10</sub> = (100011 0100) Gray code

# 1.22.2 Binary to Gray code conversion:

- The most significant bit (MSB) in the Gray code is same as the corresponding bit in the binary number

- Going from left to right, add each adjacent pair of binary bit to get the next Gray code bit and discard the carry.

Example:

Convert  $(1011)_2$  to Gray code

| Step 1 | 1 0 1 1<br>↓ | Binary |                            |

|--------|--------------|--------|----------------------------|

|        | 1            | Gray   |                            |

| Step 2 | 1+0 1 1      | Binary | (1011) (1110)              |

|        | 1 1          | Gray   | $(1011)_2 = (1110)_{Gray}$ |

| Step 3 | 1 0+1 1      | Binary |                            |

|        | 1 1 1        | Gray   |                            |

| Step 4 | 1 0 1+1      | Binary |                            |

|        | 1 1 1 0      | Gray   |                            |

# 1.22.3 Grayto Binarycode conversion:

- The most significant bit (MSB) in the Binary code is same as the corresponding bit in the Gray code

- Going from left to right, add each binary bit generated to the gray digit in the next adjacent position and discard the carry.

Example:

|        | c - Juliuy                                            |        |                            |

|--------|-------------------------------------------------------|--------|----------------------------|

| Step 1 | 1 110<br>I                                            | Gray   |                            |

|        | *<br>1<br>\_+                                         | Binary |                            |

| Step 2 | 1 110                                                 | Gray   |                            |

|        | $\downarrow$                                          | Binary |                            |

| Step 3 | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | Gray   | $(1110)_{Gray} = (1011)_2$ |

|        | $\bigvee$                                             | Binary |                            |

| Step 4 |                                                       | Gray   |                            |

|        | $\begin{array}{cccccccccccccccccccccccccccccccccccc$  | Binary |                            |

Convert  $(1110)_{Gray}$  to Binary code

# 1.23 Alphanumeric code:

Alphanumeric codes are also called character codes due to their certain properties. These codes are basically binary. These codes are used to write alphanumeric data, including data, letters of the alphabet, numbers, mathematical symbols and punctuation marks which can be easily understandable and can be processed by the computers. Input output devices such as keyboards, monitors, mouse can be interfaced using these codes. A complete alphanumeric code would include the 26 lowercase letters , 26 uppercase letters, 10 numeric digits, 7 punctuation marks and anywhere from 20 to 40 other characters such as +, /, \*, # and so on. That is it represents all of the various characters and functions that are found on a standard typewriter or computer keyboard. The most common alphanumeric codes used are ASCII code, EBCDIC code and Unicode.

## 1.23.1 ASCII code

The full form of ASCII code is American Standard Code for Information Interchange. It is a seven bit code based on the English alphabet. In 1967 this code was first published and since then it is being modified and updated. ASCII code has 128 characters some of which are enlisted below to get familiar with the code.

| Dec | Octal | Hex | Binary   | Symbol | Description         |

|-----|-------|-----|----------|--------|---------------------|

| 1   | 001   | 01  | 0000001  | SOH    | Start of Heading    |

| 2   | 002   | 02  | 00000010 | STX    | Start of text       |

| 3   | 003   | 03  | 00000011 | ETX    | End of text         |

| 4   | 004   | 04  | 00000100 | EOT    | End of transmission |

| 5   | 005   | 05  | 00000101 | ENQ    | Enquiry             |

| 6   | 006   | 06  | 00000110 | АСК    | Acknowledgement     |

| 7   | 007   | 07  | 00000111 | BEL    | Bell                |

| 8   | 010   | 08  | 00001000 | BS     | Back Space          |

| 9   | 011   | 09  | 00001001 | HT     | Horizontal Tab      |

| 10  | 012   | 0A  | 00001010 | LF     | Line Feed           |

| 11  | 013   | OB  | 00001011 | VT     | Vertical Tab        |

| 12  | 014   | 0C  | 00001100 | FF     | Form Feed           |

| 13  | 015   | 0D  | 00001101 | CR     | Carriage Return     |

| 14  | 016   | 0E  | 00001110 | SO     | Shift Out/X-On      |

| 15  | 017   | OF  | 00001111 | SI     | Shift In/X-O        |

Example:

The following is a message encoded in ASCII code. What is the message? 01001000 1000101 1001100 1010000 Solution: Convert each 7 bit code to its Hexadecimal equivalent С The result are 48 45 4C 50

Locate these hexadecimal values in table ASCII and determine the character represented by each. The result are: H E L P

#### 1.23.2 EBCDIC code:

The EBCDIC stands for Extended Binary Coded Decimal Interchange Code. IBM invented this code to extend the Binary Coded Decimal which existed at that time. All the IBM computers and peripherals use this code. It is an 8 bit code and therefore can accommodate 256 characters. Below is given some characters of EBCDIC code to get familiar with it.

| Char | EBCDIC    | нех | Char | EBCDIC    | нех | Char  | EBCDIC    | нех |

|------|-----------|-----|------|-----------|-----|-------|-----------|-----|

| А    | 1100 0001 | C1  | Р    | 1101 0111 | D7  | 4     | 1111 0100 | F4  |

| в    | 1100 0010 | C2  | Q    | 1101 1000 | D8  | 5     | 1111 0101 | F5  |

| с    | 1100 0011 | C3  | R    | 1101 1001 | D9  | 6     | 1111 0110 | F6  |

| D    | 1100 0100 | C4  | s    | 1110 0010 | E2  | 7     | 1111 0111 | F7  |

| E    | 1100 0101 | C5  | т    | 1110 0011 | E3  | 8     | 1111 1000 | F8  |

| F    | 1100 0110 | C6  | U    | 1110 0100 | E4  | 9     | 1111 1001 | F9  |

| G    | 1100 0111 | C7  | V    | 1110 0101 | E5  | blank |           |     |

| н    | 1100 1000 | C8  | w    | 1110 0110 | E6  | •     |           |     |

| I    | 1100 1001 | C9  | x    | 1110 0111 | E7  | (     |           |     |

| J    | 1101 0001 | D1  | Y    | 1110 1000 | E8  | +     |           |     |

| к    | 1101 0010 | D2  | z    | 1110 1001 | E9  | \$    |           |     |

| L    | 1101 0011 | D3  | 0    | 1111 0000 | FO  | *     |           |     |

| М    | 1101 0100 | D4  | 1    | 1111 0001 | F1  | )     |           |     |

| N    | 1101 0101 | D5  | 2    | 1111 0010 | F2  | -     |           |     |

| 0    | 1101 0110 | D6  | 3    | 1111 0011 | F3  | /     |           |     |

# 1.24.3 Unicode

Unicode is the newest concept in digital coding. In Unicode every number has a unique character. Leading technological giants have adopted this code for its uniqueness.

# Boolean operation-rules and laws of Boolean algebra-Demorgan's theorem-implications of expression using Boolean algebra-Karnaugh map

## 2.1 Boolean algebra:

Boolean algebra or switching algebra is a system of mathematical logic to perform different mathematical operations in binary system. Boolean algebra which was formulated by George Boole, an English mathematician (1815-1864) described propositions whose outcome would be either *true or false*. There only three basis binary operations, AND, OR and NOT by which all simple as well as complex binary mathematical operations are to be done. There are many rules in Boolean algebra by which those mathematical operations are done. In Boolean algebra, the variables are represented by English Capital Letter like A, B, C,etc. and the value of each variable can be either 1 or 0, nothing else. In Boolean algebra an expression given can also be converted into a logic diagram using different logic gates like AND gate, OR gate and NOT gate, NOR gates, NAND gates, XOR gates, XNOR gates etc. Some basic logical Boolean operations:

| AND Operation | OR Operation | NOT Operation      |

|---------------|--------------|--------------------|

| 0.0 = 0       | 0 + 0 = 0    | $\overline{1} = 0$ |

| 0.1 = 0       | 0 + 1 = 0    | $\overline{0} = 1$ |

| 1.0 = 0       | 1 + 0 = 0    | 0 = 1              |

| 1.1 = 1       | 1 + 1 = 1    |                    |

#### 2.2 Some Basic laws for Boolean Algebra:

#### 2.2.1 Boolean Postulates:

- 1.  $A \cdot 0 = 0$  where A can be either 0 or 1.

- 2.  $A \cdot 1 = AwhereAcanbeeither 0 \text{ or } 1.$

- 3.  $A \cdot A = A where A can be either 0 or 1.$

- 4.  $A \cdot \overline{A} = 0$  where A can be either 0 or 1.

- 5.  $\overline{\overline{A}} = AwhereAcanbeeither 0 or 1.$

- 6. A + 0 = AwhereAcanbeeither 0 or 1.

- 7. A + 1 = 1 where A can be either 0 or 1.

- 8.  $A + \bar{A} = 1$

9. A + A = A

10. A + B = B + A where A and B can be either 0 or 1.

11. A . B = B . A where A and B can be either 0 or 1.

12. 0 = 1, 1 = 0; if A = 1 then Ā = 0 and if A = 0 then Ā = 1

# 2.2.2 Boolean Laws:

1. Commutative Law: According to Commutative Law, the order of OR operations and AND operations conducted on the variables makes no differences.

(a)

$$A + B = B + A$$

(b)  $AB = BA$

2. Associate Law: This law is for several variables, where the OR operation of the variables result is same though the grouping of the variables different. This law is quite same in case of AND operators.

(a)

$$(A + B) + C = A + (B + C)$$

(b)  $(AB) C = A (BC)$

3. Distributive Law: This law is composed of two operators, AND and OR.

(a)

$$A (B + C) = AB + AC$$

(b)  $A + (BC) = (A + B) (A + C)$

4. Identity Law

(a)

$$A + A = A$$

(b)  $AA = A$

5. Redundance Law

- a) A + AB = A

- b) A(A + B) = A

- c)  $AB + A\overline{B} = A$

- d)  $A(\bar{A} + B) = AB$

- e)  $A + \overline{AB} = A + B$

- f)  $(A + B)(A + \bar{B}) = A$

6. De Morgan's Theorem

- a)  $(\overline{A+B}) = \overline{A}\overline{B}$

- b)  $(\overline{AB}) = \overline{A} + \overline{B}$

The laws of Boolean algebra are also true for more than two variables.

Let us show one use of this law to prove the expression A + B. C = (A + B). (A + C)Proof:

A + BC = A.1 + B.C (since, A.1 = A)= A. (1 + B) + B.C (since, B + 1 = 1) = A. (1 + C) + AB + BC (since, A.A = A.1 = A) = A. 1 + AB + BC = A(A + C) + B(A + C) = (A + B)(A + C)

Proof of De Morgan's Theorem by truth table,

$$\overline{A+B} = \overline{A} \cdot \overline{B}$$

$$\overline{A \cdot B} = \overline{A} + \overline{B}$$

| Inp | uts | Οι | Outputs        |                  |                         |                        |                     |  |

|-----|-----|----|----------------|------------------|-------------------------|------------------------|---------------------|--|

| А   | В   | Ā  | $\overline{B}$ | $\overline{A+B}$ | $\bar{A} \cdot \bar{B}$ | $\overline{A \cdot B}$ | $\bar{A} + \bar{B}$ |  |

| 0   | 0   | 1  | 1              | 1                | 1                       | 1                      | 1                   |  |

| 0   | 1   | 1  | 0              | 0                | 0                       | 1                      | 1                   |  |

| 1   | 0   | 0  | 1              | 0                | 0                       | 1                      | 1                   |  |

| 1   | 1   | 0  | 0              | 0                | 0                       | 0                      | 0                   |  |

Column for  $\overline{A + B}$  and  $\overline{AB}$  are same Column for  $\overline{AB}$  and  $\overline{A} + \overline{B}$  are same

cotanti j or HD ana H | D are sand

2.3 Examples of Boolean Algebra:

1. Simplify,

$$\overline{(A + \overline{B})(C + \overline{D})}$$

$\overline{(A + \overline{B})(C + \overline{D})} = \overline{(A + \overline{B})} + \overline{(C + \overline{D})}$

$= \overline{A} \cdot \overline{B} + \overline{C} \cdot \overline{D}$

$= \overline{AB} + \overline{CD}$

There is another method of simplifying complex Boolean expression. In this method there are only three simple steps.

- i. Complement entire Boolean expression.

- ii. Change all ORs to ANDs and all ANDs to ORs.

- iii. Complement each of the variables and get final expression.

By this method,

Step 1:  $\overline{(A + \overline{B})(C + \overline{D})}$  will be first complemented, we get  $(A + \overline{B})(C + \overline{D})$

Step 2: Change all (+) to (.) and (.) to (+) , we get  $A\overline{B} + C\overline{D}$

Step 3: complement each of the variable, we get  $\overline{AB} + \overline{CD}$

The final simplified form of Boolean expression  $\overline{(A + \overline{B})(C + \overline{D})}$  is got at the third step.

And it is exactly equal to the results which have been got by applying De Morgan Theorem.

2. Simplify,  $\overline{AB} + \overline{A} + AB$  $\overline{AB} + \overline{A} + AB$ ) =  $\overline{AB} \cdot \overline{A} \cdot \overline{AB}$ =  $AB \cdot A \cdot \overline{AB}$ = 0 By Second Method,

$\overline{\overline{AB} + \overline{A} + AB} = \overline{AB} + \overline{A} + AB = \overline{A + B} \cdot \overline{A} \cdot A + B = \overline{\overline{A} + \overline{B}} \cdot A \cdot \overline{A} + \overline{B} = 0$

3. Simplify,  $AB + A\overline{B}C + B\overline{C}$   $AB + A\overline{B}C + B\overline{C} = A(B + \overline{B}C) + B\overline{C}$   $= A(B + \overline{B})(B + C) + B\overline{C}$   $= AB + AC + B\overline{C}$  Since  $B + \overline{B} = 1$   $= AB(C + \overline{C}) + AC + B\overline{C}$   $= ABC + AB\overline{C} + AC + B\overline{C}$   $= AC(1 + B) + B\overline{C}(A + 1)$  $= AC + B\overline{C}$  4. Simplify,  $C + \overline{BC}$ :

| <u>Expression</u>           | <u>Rule(s) Used</u>            |

|-----------------------------|--------------------------------|

| $C + \overline{BC}$         | Original Expression            |

| $= C + (\bar{B} + \bar{C})$ | DeMorgan's Law.                |

| $= (C + \bar{C}) + \bar{B}$ | Commutative, Associative Laws. |

| = 1 + B                     | Complement Law.                |

| = 1                         | Identity Law.                  |

5. Simplify

$$\overline{AB}\overline{C} + \overline{AB}\overline{C} + A\overline{B}\overline{C} + A\overline{B}\overline{C}$$

$\overline{AB}\overline{C} + \overline{AB}\overline{C} + A\overline{B}\overline{C} + A\overline{B}\overline{C} = \overline{A}\overline{C}(\overline{B} + B) + A\overline{C}(\overline{B} + B)$

$= \overline{A}\overline{C} + A\overline{C}$  Since  $\overline{B} + B = 1$

$= \overline{C}(\overline{A} + A)$

$= \overline{C}$

6. Simplify,  $(A + C)(AD + A\overline{D}) + AC + C$ :

| Rule(s) Used                        |

|-------------------------------------|

| Original Expression                 |

| Distributive.                       |

| Complement, Identity.               |

| Commutative, Distributive.          |

| Associative, Idempotent.            |

| Distributive.                       |

| Idempotent, Identity, Distributive. |

| Identity, twice.                    |

|                                     |

7. Simplify:  $\bar{A}(A + B) + (B + AA)(A + \bar{B})$ :

| $\frac{\text{Expression}}{\bar{A}(A + B) + (B + AA)(A + \bar{B})}$ | <u>Rule(s) Used</u><br>Original Expression                                                                                |  |  |  |  |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| $= \overline{A}A + \overline{A}B + (B + A)A + (B + A)\overline{B}$ | Idempotent (AA to A), then<br>Distributive, used twice.                                                                   |  |  |  |  |

| $= \overline{A}B + (B + A)A + (B + A)\overline{B}$                 | Complement, then Identity.<br>(Strictly speaking, we also used the<br>Commutative Law for each of these<br>applications.) |  |  |  |  |

| $= \bar{A}B + BA + AA + B\bar{B} + A\bar{B}$                       | Distributive, two places.                                                                                                 |  |  |  |  |

| $= \bar{A}B + BA + A + A\bar{B}$                                   | Idempotent (for the A's), then<br>Complement and Identity to<br>remove BB.                                                |  |  |  |  |

| $= \bar{A}B + AB + A1 + A\bar{B}$                                  | Commutative, Identity; setting up for the next step.                                                                      |  |  |  |  |

| $= \bar{A}B + A(B + 1 + \bar{B})$                                  | Distributive.                                                                                                             |  |  |  |  |

| $= \overline{A}B + A$                                              | Identity, twice (depending how you count it).                                                                             |  |  |  |  |

| $= A + \overline{A}B$                                              | Commutative.                                                                                                              |  |  |  |  |

| $= (A + \overline{A})(A + B)$                                      | Distributive.                                                                                                             |  |  |  |  |

| = A + B                                                            | Complement, Identity.                                                                                                     |  |  |  |  |

8. Simplify,  $\overline{AB}(\overline{A} + B)(\overline{B} + B)$ :

| <u>Expression</u>                                   | Rule(s) Used                  |

|-----------------------------------------------------|-------------------------------|

| $\overline{AB}(\overline{A} + B)(\overline{B} + B)$ | Original Expression           |

| $= \overline{AB}(\overline{A} + B)$                 | Complement law, Identity law. |

| $= (\bar{A} + \bar{B})(\bar{A} + B)$                | DeMorgan's Law                |

| $= \overline{A} + \overline{B}B$                    | Distributive law.             |

| $= \bar{A}$                                         | Complement, Identity.         |

9. Prove that

$$(A + B)(A\overline{C} + C)(\overline{B} + AC) = A\overline{B}C + AC$$

$= (A.A\overline{C} + A.C + B.A\overline{C} + BC)(\overline{B} + AC)$

$= A\overline{B}\overline{C} + A\overline{C}.AC + A\overline{B}C + AC + AB\overline{C}.\overline{B} + AB\overline{C}.AC + BC.\overline{B} + BC.AC$

$= A\overline{B}\overline{C} + A\overline{C}(AC + ABC + ABC)$

$= A\overline{B}\overline{C} + AC(\overline{B} + 1) + ABC$

$= A\overline{B}\overline{C} + AC + ABC$

$= A\overline{B}\overline{C} + AC(1 + BC)$

$= A\overline{B}\overline{C} + AC$

$= A(C + \overline{C}\overline{B})$

$= A(C + \overline{B})$

$= AC + A\overline{B}$

#### 2.4 Representation of Boolean function in truth table:

Boolean algebra deals with binary variables and logic operation. A Boolean function, which is described by an algebraic expression called Boolean expression and which consists of binary variables, the constants 0 and 1, and the logic operation symbols. Consider the following example.

$$\underbrace{F(A, B, C, D)}_{BooleanFunction} = \underbrace{A + \overline{BC} + ADC}_{BooleanExpression}$$

Equation 1

The left side of the equation represents the output Y. So we can state equation 1 as

$$Y = A + \overline{BC} + ADC$$

Truth Table Formation

A truth table represents a table having all combinations of inputs and their corresponding result. It is possible to convert the switching equation into a truth table. For example, consider the following switching equation.

$$F(A, B, C) = A + BC$$

The output will be high (1) if A = 1 or BC = 1 or both are 1. The truth table for this equation is given by Table (2.1). The number of rows in the truth table is  $2^n$  where n is the number of input variables (n = 3 for the given equation). Hence there are  $2^3 = 8$  possible input combinations of inputs.

| Inputs |   | Output |    |            |

|--------|---|--------|----|------------|

| А      | В | С      | ВC | F = A + BC |

| 0      | 0 | 0      | 0  | 0          |

| 0      | 0 | 1      | 0  | 0          |

| 0      | 1 | 0      | 0  | 0          |

| 0      | 1 | 1      | 1  | 1          |

| 1      | 0 | 0      | 0  | 1          |

| 1      | 0 | 1      | 0  | 1          |

| 1      | 1 | 0      | 0  | 1          |

| 1      | 1 | 1      | 1  | 1          |

Table 2.1: Truth table for F = A + BC

Represent the Boolean function  $F(A, B, C) = \overline{AB} + \overline{B}C$  as truth table in table 2.2.

| А | В | С | Ā | $\overline{B}$ | ĀΒ | ĒС | $\bar{A}B + \bar{B}C$ |

|---|---|---|---|----------------|----|----|-----------------------|

| 0 | 0 | 0 | 1 | 1              | 0  | 0  | 0                     |

| 0 | 0 | 0 | 1 | 1              | 0  | 1  | 1                     |

| 0 | 1 | 0 | 1 | 0              | 1  | 0  | 1                     |

| 0 | 1 | 1 | 1 | 0              | 1  | 0  | 1                     |

| 1 | 0 | 0 | 0 | 1              | 0  | 0  | 0                     |

| 1 | 0 | 1 | 0 | 1              | 0  | 1  | 1                     |

| 1 | 1 | 0 | 0 | 0              | 0  | 0  | 0                     |

| 1 | 1 | 1 | 0 | 0              | 0  | 0  | 0                     |

Table 2.2: Truth table for  $F = \overline{AB} + \overline{B}C$

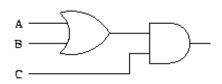

# 2.5 Logic gates using Boolean Expressions:

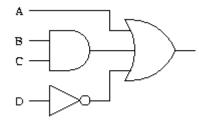

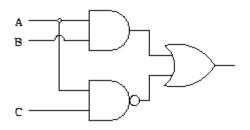

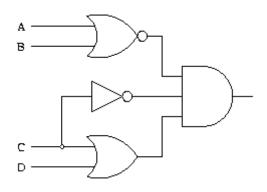

1. Draw a logic circuit for (A + B)C.

2. Draw a logic circuit for  $A + BC + \overline{D}$ .

3. Draw a logic circuit for  $AB + \overline{AC}$ .

4. Draw a logic circuit for  $(\overline{A + B}) (C + D) \overline{C}$ .

## 2.6 Minterms:

In general, the unique algebraic expression for any Boolean function can be obtained from its truth table by using an OR operator to combined all minterms for which the function is equal to 1.

A minterm, denoted as  $m_i$ , where  $0 \le i < 2^n$ , is a product (AND) of the n variables in which each variable is complemented if the value assigned to it is 0, and uncomplemented if it is 1.

1-minterms = minterms for which the function F = 1.

0-minterms = minterms for which the function F = 0.

Any Boolean function can be expressed as a sum (OR) of its 1- minterms.

A shorthand notation:

$$F(\text{list of variables}) = \sum(\text{list of } 1 - \text{minterm indices})$$

Example :

| x | у | Ζ | Minterms         | F | F' |

|---|---|---|------------------|---|----|

| 0 | 0 | 0 | $m_0 = x' y' z'$ | 0 | 1  |

| 0 | 0 | 1 | $m_1 = x' y' z$  | 0 | 1  |

| 0 | 1 | 0 | $m_2 = x' y z'$  | 0 | 1  |

| 0 | 1 | 1 | $m_3 = x' y z$   | 1 | 0  |

| 1 | 0 | 0 | $m_4 = x y' z'$  | 0 | 1  |

| 1 | 0 | 1 | $m_5 = x y' z$   | 1 | 0  |

| 1 | 1 | 0 | $m_6 = x y z'$   | 1 | 0  |

| 1 | 1 | 1 | $m_7 = x y z$    | 1 | 0  |

$$F = x'yz + xy'z + xyz' + xyz$$

$= m_3 + m_5 + m_6 + m_7$

or

$F(x, y, z) = \Sigma(3, 5, 6, 7)$

The inverse of the function can be expressed as a sum (OR) of its 0- minterms.

A shorthand notation:

$$F'(list of variables) = \Sigma(list of 0 - minterm indices)$$

Example:

$$F' = x' y' z' + x' y' z + x' y z' + x y' z'$$

=  $m_0 + m_1 + m_2 + m_4$

Or

$$F'(x, y, z) = \Sigma(0, 1, 2, 4)$$

Problem:

1. Express the Boolean function F = x + y z as a sum of minterms.

Solution:

This function has three variables: x, y, and z. Therefore All terms must have these three variables. Thus, we need to expand the first term by ANDing it with (y + y')(z + z'), and we expand the second term with (x + x') to get

$$F = x + yz = x (y + y') (z + z') + (x + x') yz$$

=  $x yz + x yz' + x y'z + x y'z' + x yz + x' yz$

=  $x' yz + x y'z' + x y'z + x yz' + x yz$

=  $m3 + m4 + m5 + m6 + m7$

=  $\Sigma(3, 4, 5, 6, 7)$

| x | у | Ζ | Minterms         | F |

|---|---|---|------------------|---|

| 0 | 0 | 0 | $m_0 = x' y' z'$ | 0 |

| 0 | 0 | 1 | $m_1 = x' y' z$  | 0 |

| 0 | 1 | 0 | $m_2 = x' y z'$  | 0 |

| 0 | 1 | 1 | $m_3 = x' y z$   | 1 |

| 1 | 0 | 0 | $m_4 = x y' z'$  | 1 |

| 1 | 0 | 1 | $m_5 = x y' z$   | 1 |

| 1 | 1 | 0 | $m_6 = x y z'$   | 1 |

| 1 | 1 | 1 | $m_7 = x y z$    | 1 |

2. Suppose a function F is defined by the following truth table, then convert it into the sum of minterms

Solution:

Given Truth Table

| Α | В | С | m.t   | F |

|---|---|---|-------|---|

| 0 | 0 | 0 | $m_0$ | 0 |

| 0 | 0 | 1 | $m_1$ | 1 |

| 0 | 1 | 0 | $m_2$ | 1 |

| 0 | 1 | 1 | $m_3$ | 0 |

| 1 | 0 | 0 | $m_4$ | 1 |

| 1 | 0 | 1 | $m_5$ | 0 |

| 1 | 1 | 0 | $m_6$ | 0 |

| 1 | 1 | 1 | $m_7$ | 1 |

Since F = 1 on rows 1, 2, 4, and 7, we obtain

$$F = m_1 + m_2 + m_4 + m_7$$

$= \bar{A}\bar{B}C + \bar{A}B\bar{C} + A\bar{B}\bar{C} + ABC$

A compact notation is to write only the numbers of the minterms included in F, using the Greek letter capital sigma to indicate a sum:

$$F = \sum (1, 2, 4, 7)$$

This form can be written down immediately by inspection of the truth table.

## 2.7 Maxterms:

A maxterm, denoted as  $M_i$ , where  $0 \le i < 2^n$ , is a sum (OR) of the *n*variables (literals) in which each variable is complemented if thevalue assigned to it is 1, and uncomplemented if it is 0.

1-maxterms = maxterms for which the function F = 1.

0-maxterms = maxterms for which the function F = 0.

Any Boolean function can be expressed as a product (AND) of its 0-maxterms.

A shorthand notation:

$$F(list of variables) = \prod(list of 0 - maxterm indices)$$

| x | у | Ζ | Maxterms             | F | F' |

|---|---|---|----------------------|---|----|

| 0 | 0 | 0 | $M_0 = x + y + z$    | 0 | 1  |

| 0 | 0 | 1 | $M_1 = x + y + z'$   | 0 | 1  |

| 0 | 1 | 0 | $M_2 = x + y' + z$   | 0 | 1  |

| 0 | 1 | 1 | $M_3 = x + y' + z'$  | 1 | 0  |

| 1 | 0 | 0 | $M_4 = x' + y + z$   | 0 | 1  |

| 1 | 0 | 1 | $M_5 = x' + y + z'$  | 1 | 0  |

| 1 | 1 | 0 | $M_6 = x' + y' + z$  | 1 | 0  |

| 1 | 1 | 1 | $M_7 = x' + y' + z'$ | 1 | 0  |

Example:

$$F = (x + y + z) \cdot (x + y + z') \cdot (x + y' + z) \cdot (x' + y + z)$$

=  $M_0 \cdot M_1 \cdot M_2 \cdot M_4$

or

$F(x, y, z) = \prod(0, 1, 2, 4)$

The inverse of the function can be expressed as a product (AND) of its 1-maxterms.

A shorthand notation:

$$F(\text{list of variables}) = \prod(\text{list of } 1 - \text{maxterm indices})$$

Example:

$$F' = (x + y' + z') \cdot (x' + y + z') \cdot (x' + y' + z) \cdot (x' + y' + z')$$

=  $M_3 \cdot M_5 \cdot M_6 \cdot M_7$

or

$F'(x, y, z) = \prod (3, 5, 6, 7)$

Problem:

1. Express the Boolean function F = xy + x'z in a product of maxterm form Solution:

Convert the function into OR terms using the distributive law.

$$F = xy + x'z$$

=  $(xy + x')(xy + z)$

=  $(x + x')(y + x')(x + z)(y + z)$

=  $(y + x')(x + z)(y + z)$

The function has three variables x, y and z. In each OR term one variable is missing

$$x' + y = x' + y + zz' = (x' + y + z)(x' + y + z')$$

$$x + z = x + z + yy' = (x + z + y)(x + z + y')$$

$$y + z = y + z + xx' = (y + z + x)(y + z + x')$$

Combining all terms and remove the terms that appear more than once, we get

$$F = (x' + y + z)(x' + y + z')(x + z + y)(x + z + y')$$

$$F = (x + y + z)(x + y' + z)(x' + y + z)(x' + y + z')$$

$$F = M_0 M_2 M_4 M_5$$

$$F(x, y, z) = \prod(0, 2, 4, 5)$$

2. Find the product of maxterms if  $F(A, B, C) = \sum (1,4,5,6)$ Solution:

For

$$F(A, B, C) = \sum (1, 4, 5, 6),$$

the complement is  $F'(A, B, C) = \sum (0,2,3) = m_0 + m_2 + m_3$

Applying DeMorgan's theorem

$$\overline{F}'(A, B, C) = \overline{m_0 + m_2 + m_3}$$

$$= \overline{m_0} \cdot \overline{m_2} \cdot \overline{m_3}$$

$$= M_0 \cdot M_2 \cdot M_3$$

$$F(A, B, C) = \prod (0, 2, 3)$$

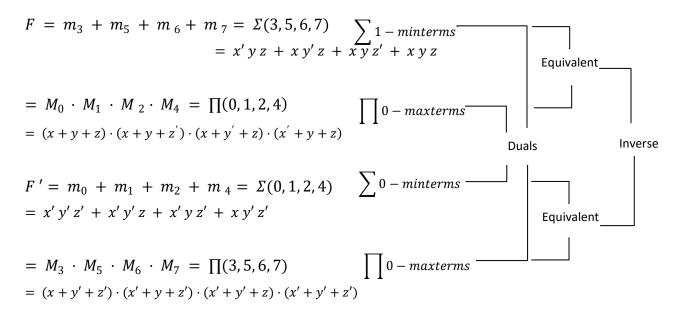

## 2.8 Canonical form :

Definition:

Any Boolean function that is expressed as a sum of minterms or as a product of maxterms is said to be in its canonical form.

To convert from one canonical form to its other equivalentform, interchange the symbols  $\sum and \prod$ , and list the index numbers that were excluded from the original form.

To convert from one canonical form to its dual, interchange the symbols  $\Sigma$  and  $\Pi$ , and list the index numbers from the original form, or use De Morgan's Law or the duality principle.

Example:

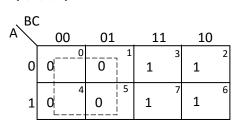

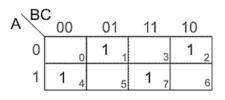

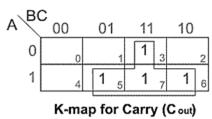

#### 2.9 Karnaugh-map or K-map:

The Boolean theorems and the De-Morgan's theorems are useful in manipulating the logic expression. We can realize the logical expression using gates. The number of logic gates required for the realization of a logical expression should be reduced to a minimum possible value. One of the methods used to minimize the logical expression is K-map method. A Karnaugh map provides a pictorial method of grouping together expressions with common factors and therefore eliminating unwanted variables. The Karnaugh map can also be described as a special arrangement of a truth table.

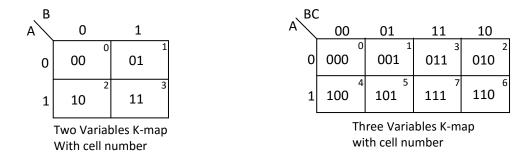

The K-map is a graphical device used to simplify a logical equation or to convert a truth table to its corresponding logic circuit in a simple, logical method. It is also known as Veitch diagram. A K-map is a diagram made up of squares and may be considered to be the graphic representation of the minterm canonical form. Each minterm is represented by a cell, and the cells are assembled in an orderly arrangement such that adjacent cell represent minterms which differ by one variable. The number of cells in a K-map depends upon the number of variables in the Boolean expression. Two variables map contain four cells, three variables map contain eight cells and n variables map contain 2<sup>n</sup> cells. Each row and column of the map is assigned by 0's and 1's as shown in figure.

This method can be done in two different ways, as discussed below.

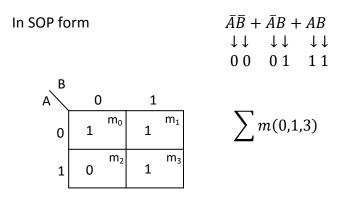

## 2.9.1 Sum of Products (SOP) Form

It is in the form of sum of three terms AB, AC, BC with each individual term is a product of two variables. Say A.B or A.C or B.C. Therefore such expressions are known as expression in SOP form. The sum and products in SOP form are not the actual additions or multiplications. In fact they are the OR and AND functions. In SOP form, 0 represents a bar and 1 represents an unbar. SOP form is represented by  $\Sigma$ .

Boolean expression in SOP may or may not be in a standard form. First the expression is converted into SOP and then, 1's are marked in each cell corresponding to the minterm of expression and the remaining cells are marked with 0's.

Examples of SOP:

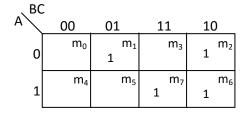

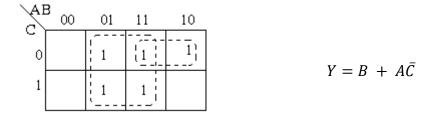

1. K-map for the Boolean expression  $Y(A, B, C) = \overline{A} + B$

Result of  $\overline{AB} + \overline{AB} + AB$  is  $\overline{A} + B$

2. K-map for the Boolean expression  $Y(A, B, C) = AB + B\overline{C} + \overline{ABC}$

| In SOP form | ABC +                              | $AB\bar{C} +$                              | $\bar{A}B\bar{C}$ +                           | ĀĒC                                        |

|-------------|------------------------------------|--------------------------------------------|-----------------------------------------------|--------------------------------------------|

|             | $\downarrow \downarrow \downarrow$ | $\downarrow\downarrow\downarrow\downarrow$ | $\downarrow \downarrow \downarrow \downarrow$ | $\downarrow\downarrow\downarrow\downarrow$ |

|             | 1 1 1                              | 11 0                                       | 01.0                                          | 001                                        |

| $\sum m(1,2,6,7)$ |  |

|-------------------|--|

Result of  $ABC + AB\overline{C} + \overline{A}B\overline{C} + \overline{A}\overline{B}C$  is  $AB + B\overline{C} + \overline{A}\overline{B}C$

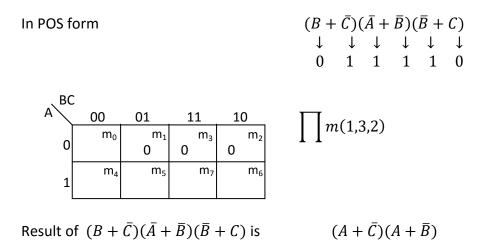

# 2.9.2 Product of Sums (POS) Form

It is in the form of product of three terms (A+B), (B+C), or (A+C) with each term is in the form of a sum of two variables. Such expressions are said to be in the product of sums (POS) form. In POS form, 0 represents an unbar and 1 represents a bar. POS form is represented by  $\prod$

Example of POS:

## 2.10 Grouping the adjacent cells of Karnaugh map:

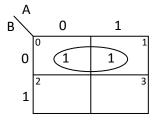

Adjacent cells: If two occupied cells of a Karnaugh are adjacent, horizontally or vertically (but not diagonally) then one variable is redundant. This has resulted by labeling the map as shown,

Consider the above map. The function plotted is  $Y = f(AB) = \overline{AB} + A\overline{B}$ Using algebraic simplification,  $Y = \overline{B}(\overline{A} + A) = \overline{B}$  by using the Boolean law $(A + \overline{A} = 1)$ . Referring to the map we can encircle the adjacent cells and assume that A and  $\overline{A}$  are not required.

i.e. adjacent cells satisfy the condition  $A + \bar{A} = 1$ .

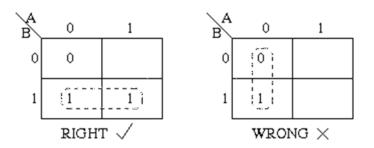

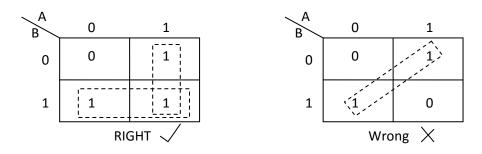

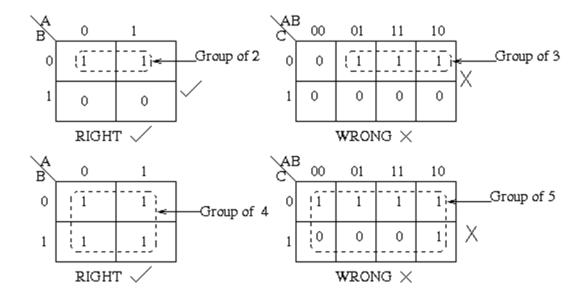

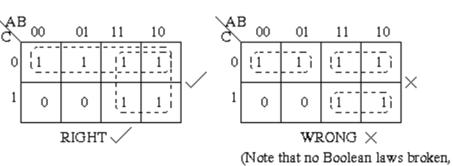

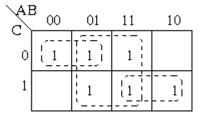

The Karnaugh map uses the following rules for the simplification of expressions by grouping together adjacent cells containing ones

# 2.11 Rules for grouping cells in K-map:

- 1. Groups may not include any cell containing a zero

- 2. Groups may be horizontal or vertical, but not diagonal.

- 3. Groups must contain 1, 2, 4, 8, or in general  $2^n$  cells. That is if n = 1, a group will contain two 1's since  $2^1 = 2$ . If n = 2, a group will contain four 1's since  $2^2 = 4$ .

- 4. Each group should be as large as possible.

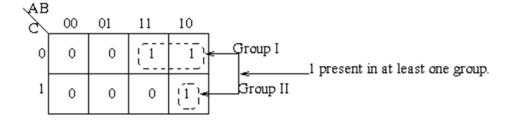

- 5. Each cell containing a one must be in at least one group.

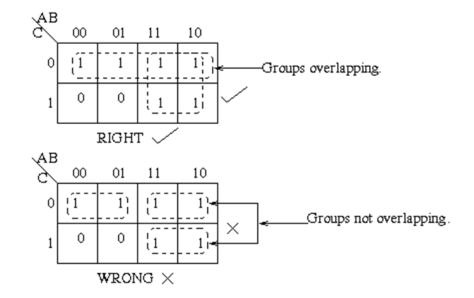

- 6. Groups may overlap.

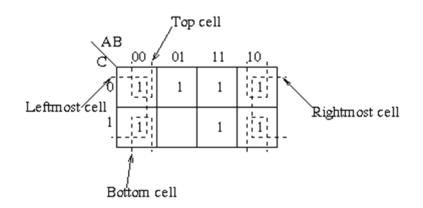

- 7. Groups may wrap around the table. The leftmost cell in a row may be grouped with the rightmost cell and the top cell in a column may be grouped with the bottom cell.

- There should be as few groups as possible, as long as this does not contradict any of the previous rules.

# 2.12 Examples for the above said rules:

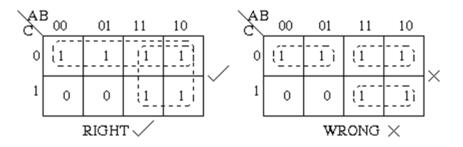

In the following examples the grouping of cells in correct method is indicated as "RIGHT with a tick mark". For more understanding, the improper grouping is also indicated about the respective rule as "Wrong with a cross mark".

For Rule 1:

For Rule 3:

For Rule 4:

but not sufficiently minimal)

# For Rule 5:

# For Rule 6:

For Rule 7:

### For Rule 8:

## 2.13Simplifying Boolean Expression using K Map

2.13.1 Minterm Solution of K Map:

The following are the steps to obtain simplified minterm solution using K-map.

Step 1: Initiate

Express the given expression in its canonical form

Step 2: Populate the K-map

Enter the value of 'one' for each product-term into the K-map cell, while filling others with zeros.

Step 3: Form Groups

Using the rules of grouping of cells form as many as possible larger groups

Step 4: Obtain Boolean Expression for Each Group

Express each group interms of input variables by looking at the common variables seenin cell-labeling.

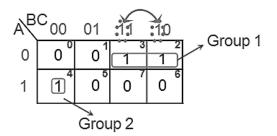

For example in the figure shown below there are two groups with two and one number of 'ones' in them (Group 1 and Group 2, respectively). All the 'ones' in the Group 1 of the K-map are present in the row for which A = 0. Thus they contain the variable  $\overline{A}$ . Further these two 'ones' are present in adjacent columns which have only B term in common as indicated by the double headed arrow in the figure.

46

Hence the next term is B. This yields the product term corresponding to this group as  $\overline{AB}$ . Similarly the 'one' in the Group 2 of the K-map is present in the row for which A = 1. Further the variables corresponding to its column are  $\overline{BC}$ . Thus one gets the overall product-term for this group as  $\overline{ABC}$ .

Step 5: Obtain Boolean Expression for the Output

The product-terms obtained for individual groups are to be combined to form sumof-product (SOP) form which yields the overall simplified Boolean expression. This means that for the K-map shown in Step 4, the overall simplified output expression is  $\bar{A} + A\bar{B}\bar{C}$

## 2.13.2 Maxterm Solution of K Map

The method to be followed in order to obtain simplified maxterm solution using K-map is similar to that for minterm solution except minor changes listed below.

- K-map cells are to be populated by 'zeros' for each sum-term of the expression instead of 'ones'.

- 2. Grouping is to be carried-on for 'zeros' and not for 'ones'.

- Boolean expressions for each group are to be expressed as sum-terms and not as product-terms.

- 4. Sum-terms of all individual groups are to be combined to obtain the overall simplified Boolean expression in product-of-sums (POS) form.

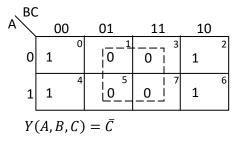

Example:  $Y = (A + B + \overline{C}) + (A + \overline{B} + \overline{C}) + (\overline{A} + \overline{B} + C) + (\overline{A} + \overline{B} + \overline{C})$

$$A = \begin{bmatrix} BC & 00 & 01 & 11 & 10 \\ 0 & 1 & 0 & 1 & 0 & 3 & 1 & 2 \\ 1 & 1 & 4 & 1 & 5 & 0 & 7 & 0 & 6 \end{bmatrix}$$

Simplified Expression is  $Y = (A + \bar{C})(\bar{A} + \bar{B})$

Problems:

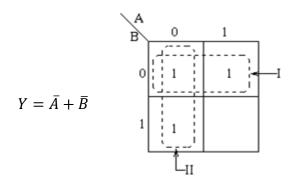

1. Draw Karnaugh map for the Boolean expression  $Y = \overline{AB} + \overline{AB} + \overline{AB}$ :

Pairs of 1's are grouped as shown above, and the simplified answer is obtained by using the following steps: Two groups can be formed that the largest rectangular bands that can bemadeconsistoftwo1s.

The first group:

The first group labeledI, consists of two 1s which correspond to A = 0, B = 0 and A = 1, B = 0. (or) all squares that correspond to the area of the map where B = 0 contains 1s, independent of the value of A. So when B = 0 the output is 1. The expression of the output will contain the term  $\overline{B}$

The second group:

The group labeledII corresponds to the area of the map where A = 0. The group can therefore be defined as $\overline{A}$ . This implies that when A = 0 contains 1s, independent of the value of B.So when A = 0 the output is 1. The expression of the output is  $\overline{A}$

Hence the simplified answer is  $Y = \overline{A} + \overline{B}$

2. Draw K-map for the Expression  $Y = \overline{ABC} + \overline{AB} + AB\overline{C} + AC$

$Y = B + AC + \bar{A}\bar{C}$

By using the rules of simplification and ringing of adjacent cells in order to make as many variables dismissed, the minimised result obtained is  $Y = B + AC + \overline{AC}$

3. Draw k-map for the expression  $Y = \overline{AB} + B\overline{C} + BC + A\overline{B}\overline{C}$

By using the rules of simplification and ringing of adjacent cells in order to make as many variables redundant, the minimised result obtained is  $Y = B + A\overline{C}$

- 4. Minimize the following expressions using K-map

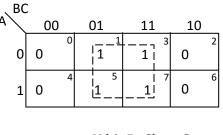

- (i)  $Y(A, B, C) = \sum m(1,3,5,7)$

- (ii)  $Y(A, B, C) = \sum m(0, 1, 4, 5)$

- (iii)  $Y(A, B, C) = \sum m(0, 2, 4, 6)$

Solution:

(i)  $Y(A, B, C) = \sum m(1,3,5,7)$

Y(A,B,C)=C

(ii)  $Y(A, B, C) = \sum m(0, 1, 4, 5)$

| A | 00    |   | 01 |   | 11 |   | 10 |   |

|---|-------|---|----|---|----|---|----|---|

| 0 | 1     | 0 | 1  | 1 | 0  | 3 | 0  | 2 |

|   | <br>_ | 4 |    | 5 |    | 7 | •  | 6 |

| 1 | 1     |   | 1  |   | 0  |   | 0  |   |

$Y(A, B, C) = \overline{B}$

(iii)  $Y(A, B, C) = \sum m(0, 2, 4, 6)$

5. Simplify the expression using K-map  $Y(A, B, C) = \sum m(0, 1, 2, 3, 4, 5, 6, 7)$

| BC             | 2 |          |   |    |   |    |   |          |   |

|----------------|---|----------|---|----|---|----|---|----------|---|

| A              |   | 00       |   | 01 |   | 11 |   | 10       |   |

|                |   | . — —    | 0 |    | 1 |    | 3 | 1        | 2 |

| 0              |   | 1        |   | 1  |   | 1  |   | $1_{1}$  |   |

|                | _ |          | 4 |    | 5 |    | 7 | -+       | 6 |

| 1              |   | 1        | - | 1  | - | 1  |   | $1_1$    | - |

|                |   | <u> </u> | _ |    |   |    | - | <u> </u> |   |

| Y(A, B, C) = 1 |   |          |   |    |   |    |   |          |   |

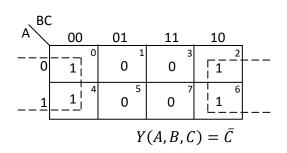

- 6. Minimize the following expressions using K-map

- (i)  $Y(A, B, C) = \prod M(1, 3, 5, 7)$

- (ii)  $Y(A, B, C) = \prod M(0, 1, 4, 5)$

- (iii)  $Y(A, B, C) = \prod M(0, 2, 4, 6)$

Solution:

(i)

$$Y(A, B, C) = \prod M(1,3,5,7)$$

(ii)  $Y(A, B, C) = \prod M(1,3,5,7)$

Y(A,B,C)=B

(iii)

$$Y(A, B, C) = \prod M(0, 2, 4, 6)$$

| A | 00 | ) | 01 |   | 11 |   | 10       |   |  |

|---|----|---|----|---|----|---|----------|---|--|

| 0 | 0  | 0 | 1  | 1 | 1  | З | б_       | 2 |  |

| 1 | _0 | 4 | 1  | 5 | 1  | 7 | <u>þ</u> | 6 |  |

Y(A,B,C)=C

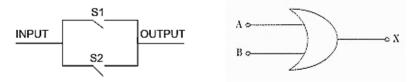

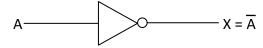

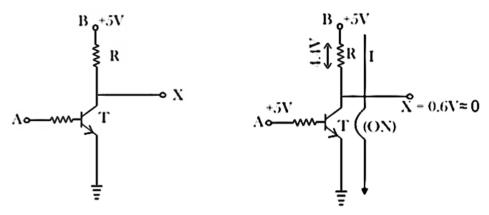

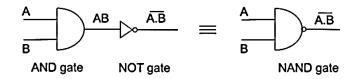

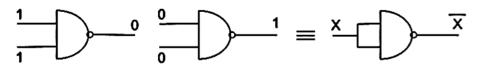

### Unit III Basic Logic Gates

AND, OR, NOT (symbol, truth table, circuit diagram, working) – NAND, NOR, EX-OR, EX-NOR(symbol, truth table)

## 3.1 Logic Gate:

A logic gate is an elementary building block from which all digital electronic circuits and microprocessor based systems are constructed.

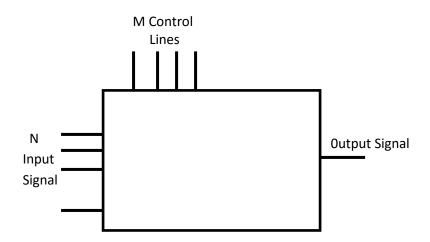

Figure 3.1 Block Diagram of Logic Gate

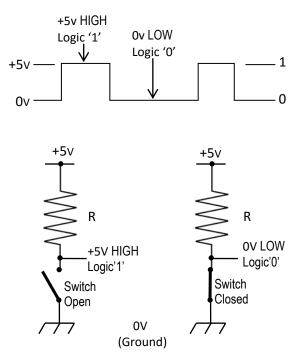

In digital logic design only two voltage levels or states are allowed and these states are generally referred to as Logic "1" and Logic "0", High and Low, or True and False. These two states are represented in Boolean algebra and standard truth tables by the binary digits of "1" and "0" respectively. Most logic gates have two inputs and one output. At any given moment, every terminal is in one of the two binary conditions low (0) or high (1), represented by different voltage levels. A good example of a digital state is a simple light switch as it is either "ON" or "OFF" but not both at the same time

It is an electronic circuit having one or more than one input and only one output. The relationship between the input and the output is based on certain logic. Based on this, logic gates are named as AND gate, OR gate, NOT gate etc. The relationship between the various digital states is given in table 3.1 as